-

Notifications

You must be signed in to change notification settings - Fork 9

OBC EM

Grzegorz Gajoch edited this page Jan 10, 2017

·

20 revisions

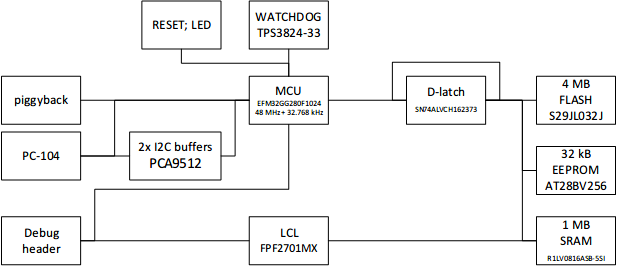

This document is containing requirements for OBC EM board.

- As substitute of OBC FM, which can be used in PC-104 stack

- (Non-)Profit!

- Same format and connector layout as on OBC FM board (PC-104, piggyback, UART dbg, ?) + dodatkowe złącze do debugowania i mockowania FPGA.

- Processor: EFM32GG280F1024

- 48 MHz + 32.768 kHz crystal oscillators

- TPS3824-33 hardware watchdog

- EBI:

- 1 MB SRAM - R1LV1616RSA-5SI

- 4 MB FLASH - S29JL032J

- 32 kB EEPROM - AT28BV256

- LCL (FPF2701MX cały czas włączony) for SRAM latchup protection

- GPIOs on debug header

- UART0 - PiggyBack header

- UART1 - UART debug connector

- I2C0 - PC104 bus (41, 43)

- I2C1 - PC104 pld (21, 23)

- EBI - multiplexed (SN74ALVCH162373), 8-bit Data, 24-bit address mode

- ADC pins as on FM, on piggyback

- ACMP0 (channel 2), ACMP1 (channel 0) - SRAM1, SRAM2 odczyty prądów SRAMów podawane z zewnętrznego generatora (żeby testować)

- GPIO:

- PD7 for power SRAM1, active high

- PD8 for power SRAM2, active high

- PC14 enable SRAM1, active low

- PC15 enable SRAM2, active low

- PF9 - watchdog kick

- PE2, PE3 - FPGA control pins

- PB0, PB1, PB2 - FPGA error pins

-

BSP_EBI_SramXPowOn-> włączenie zasilania pamięci (PD7, PD8), na pałę do LCLa -

BSP_EBI_SramXBufOn-> włączenie bufora pamięci (PC14, PC15) -

BSP_EBI_SramXFPGAOff-> kontrola FPGA - EFM <-> FPGA - 8 linii danych, 24 linie adresu

- FPGA rozszerza 8 bitów w 16 i zapisuje do obu pamięci

- dostęp do zmiennej większej niż 8 bitów wymaga kilu cykli

- Jakiś task musi chodzić cały czas i sprawdzać pamięć (domyślnie: cała pamięć na jeden raz) - tak zrobimy

- ISR -> multiple errors -> reboot, bo zbyt niebezpiecznie jest kontynuować

- Wyprowadzimy wszystkie piny związane z FPGA + sygnały sterujące z RAMu na jakiś header (najlepiej kątowy na skraju płytki + zasilanie w pobliżu)

- Masa co kawałek

- Jeden jednomegowy SRAM

- Tak, żeby dało się wylutować FLASH z programem

- Chcemy mieć ciągły dostęp do projektu. Przed ostatecznym wyprodukowaniem chcemy zobaczyć projekt.

- LCLe do pamięci wyprowadzone na header, linie kontrolujące z OBC LCLa też na header, jak będziemy chcieli, żeby OBC kontrolował pamięć to wsadzimy zworkę

- Bez buforów

- Pomiar prądu (latchup w pamięciach) na header, tak żeby można było symulować - 2 kanały

- ważne miejsce

- 2x I2C

- 3.3V

- ważne miejsce

- ważne miejsce

- V_BAT

- 3.3V

- UART

- SPI

- 13xGPIO

- Backup power domain

- JTAG + SWO

- 2xI2C

- UART

- ACMP0, ACMP1 (Pomiary prądów pamięci są podawane z zewnątrz, z generatora)

- Mock dla FPGA: GPIOs (2x włącz/wyłącz LCLe do pamięci; 2x enable do pamięci; 2xFPGA controla; 3x FPGA errors; CS, WE#, OE# for SRAM)

- 1x GPIO (Watchdog)

- Linia resetu

- Przycisk reset.

- Diody LED przypięte do linii, które nie są używane - 5-10 sztuk.

pw-sat.pl | radio.pw-sat.pl | Twitter | Facebook | Instagram

- Meeting 21.11.2015

- [Weekly 20.04.2016] (https://github.com/PW-Sat2/PWSat2OBC/wiki/Weekly-20-04-2016)

- [Weekly 4.05.2016] (https://github.com/PW-Sat2/PWSat2OBC/wiki/Weekly-4.05.2016)

- Weekly 11.05.2016

- Weekly 02.06.2016